Cours:

Circuit Microelectronique

PHY

568 (resp: Alain GREINER)

|

Année

scolaire 2005-2006

Enseignants

Y. BONNASSIEUX,

G. FONTAINE,

A. GREINER,

A. FILIPE

Sujet de la PAL 2005

Transparents

de Cours: (documents en format pdf)

Petites Classes: (documents en format pdf)

| |

Thème |

Sujet |

Corrigé |

|

PC1: |

Inverseur

CMOS- Portes Statiques |

|

CorrigePC1 |

|

PC2: |

Dessin

de masques dans les circuits intégrés CMOS |

|

CorrigePC2

Presentation |

|

PC3: |

Systèmes

numériques synchrones & synthèse des automates |

|

CorrigePC3 |

|

PC4: |

Travaux

Expérimentaux : Simulation SPICE |

voir

TP1 |

voir

TP1 |

|

PC5: |

Etude

d'un préamplificateur pour photodiode |

|

CorrigePC5 |

|

PC6: |

Dimensionnement

des transistors CMOS |

|

CorrigePC6 |

| PC7: |

Dimensionnement

d'une ROM CMOS |

|

CorrigePC7 |

| PC8: |

Travaux

Expérimentaux : CAO

ALLIANCE |

Voir TP2 |

Voir

TP2 |

|

PC9: |

Test structurel et Modèle

des collages |

|

CorrigePC9 |

Travaux

Expérimentaux :

TP1 : SPICE

TP2

: CAO

ALLIANCE

Pour en savoir plus:

Quelques outils de CAD (gratuits) à télécharger:

Bibliographie:

|

Introduction to VLSI circuits and systems, John P. Uyemura, John Wiley & son, 2002

|

|

VHDL, Langage modélisation synthèse, R. Airiau, J.M. Bergé, V. Olive, J. Rouillard, Presses Polytechniques et Universitaires Romandes, 1998

|

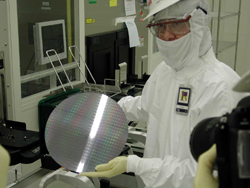

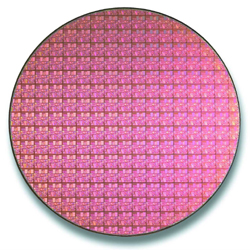

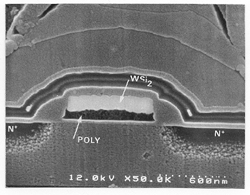

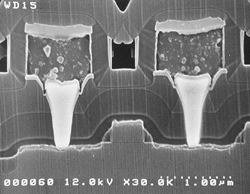

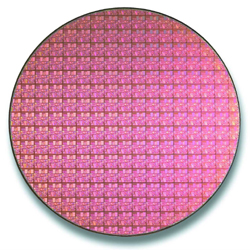

Galerie de photographies: (cliquez sur les photos pour avoir leur définition maximale)

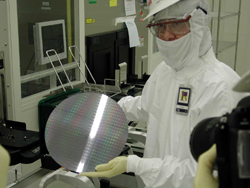

Wafer 300mm

(©Intel) |

Wafer Pentium 4

(©Intel) |

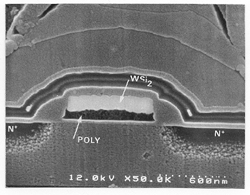

Transistor MOS

(coupe) |

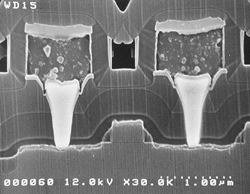

Transistor MOS

(coupe) |

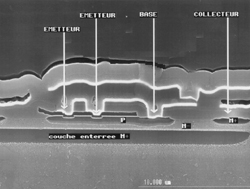

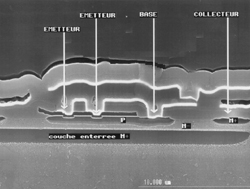

Transistor Bipolaire

(coupe) |

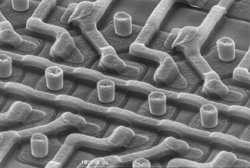

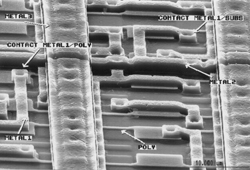

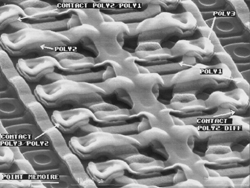

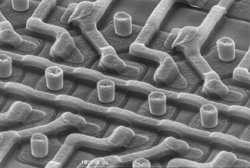

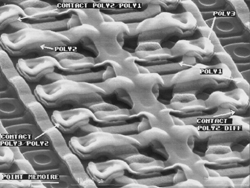

Contacts directs poly-zone active

|

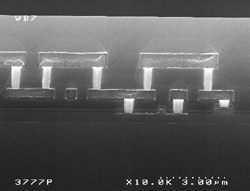

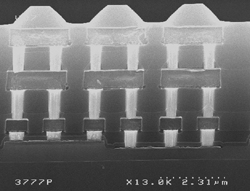

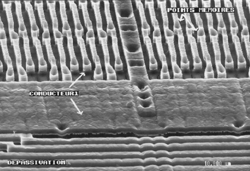

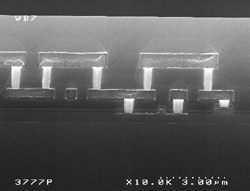

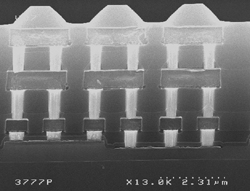

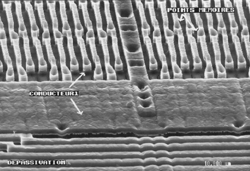

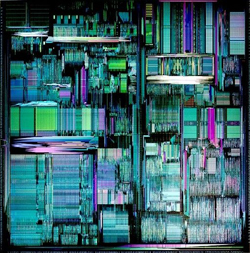

Interconnexions

(©ST) |

Interconnexions

(©ST) |

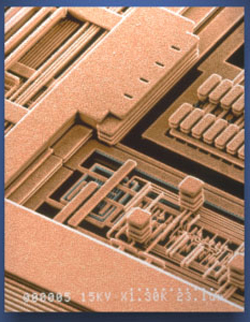

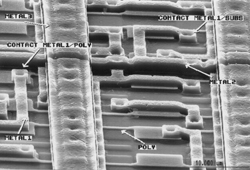

Couches d'interconnexions |

Métallisations |

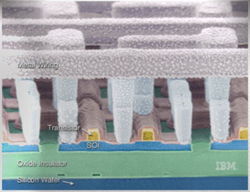

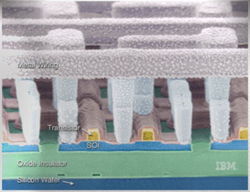

Techno SOI

(©IBM) |

Interconnexions cuivre

(©IBM) |

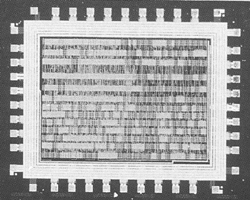

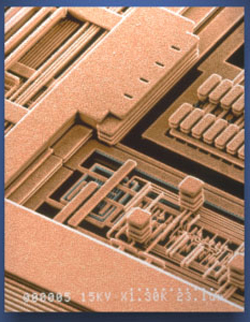

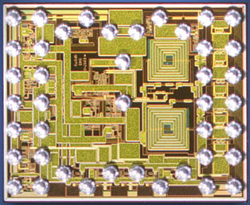

Circuit pré-caractérisé |

Point de mémoire statique 3 poly |

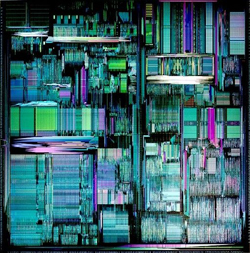

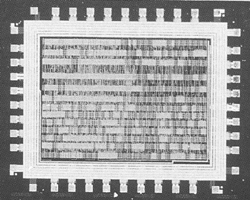

Microprocesseur en 0,35µm

(©IBM) |

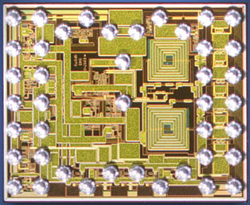

Récepteur GPS

(©IBM) |

Microprocesseur 6x86MX en boitier PGA

(©IBM) |

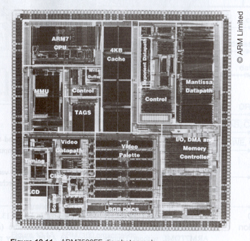

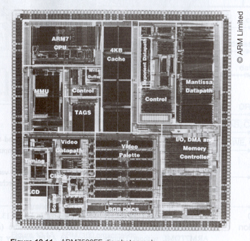

Microprocesseur ARM

(©ARM) |

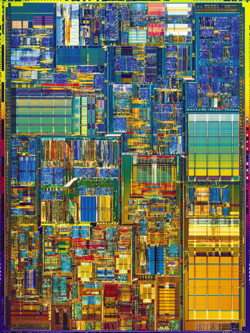

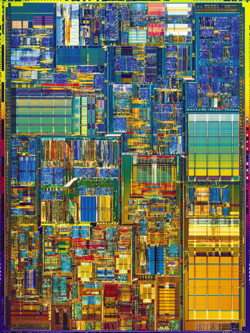

Pentium 4 (0,18µm)

(©Intel) |

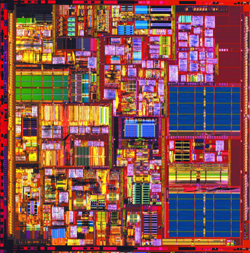

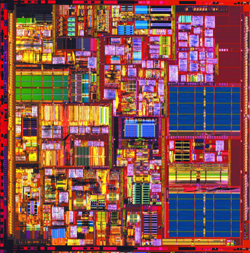

Pentium 4 (0,12µm)

(©Intel) |

Page rédigée

par: Yvan BONNASSIEUX

|